- Home

- Hardware

- SDKs

- Cloud

- Solutions

- Support

- Ecosystem

- Company

- Contact

news

Espressif Systems Represented at the 2017 Tensilica Day in Hannover

Hannover

Feb 16, 2017

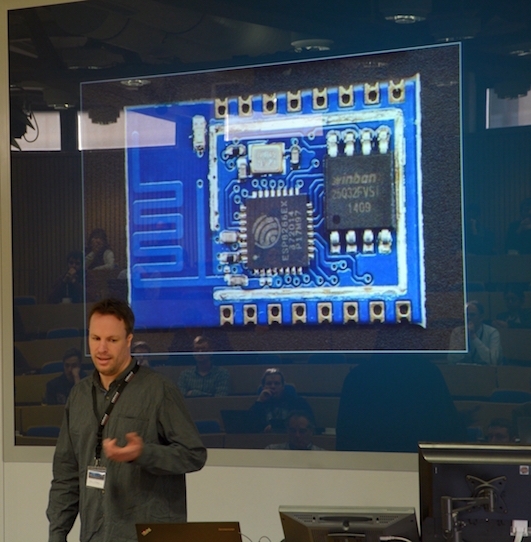

Jeroen Domburg, Software Manager and Technical Marketing Manager at Espressif Systems, was invited to the 2017 Tensilica Day Event, where he delivered a presentation entitled: "IoT on the Cheap: How Espressif Leverages Xtensa Cores".

Jeroen Domburg, Software Manager and Technical Marketing Manager at Espressif Systems, was invited to give a presentation at the 2017 Tensilica Day, which was organized by Cadence Design Systems and the Institute of Microelectronic Systems at the University of Hannover, on 16th February. The theme of this year’s workshop, which was held for the second consecutive year, was about Application Specific Instruction-Set Processors (ASIPs). Jeroen’s talk was entitled: “IoT on the Cheap: How Espressif Leverages Xtensa Cores”.

In his hour-long talk and Q&A session, Jeroen presented how Espressif Systems started in the IoT industry, and went on to discuss various technical aspects of ESP32 in light of our previous chips, ESP8089 and ESP8266. He then expanded on how ESP32 utilizes the Tensilica L106 processor.

ESP32 is a dual-core system with two Harvard Architecture Xtensa LX6 central processing units (CPUs). All embedded memory, external memory and peripherals are located on the data bus and/or the instruction bus of these CPUs. ESP32’s bluetooth specifications are recognized and certified by the Bluetooth Special Interest Group (SIG), a not-for-profit, non-stock international corporation headquartered in Kirkland, Washington, with local offices in China, South Korea, Japan, and Sweden.

To learn more about ESP32, you can click on here.

If you would like to learn more about the 2017 Tensilica Day, and download the program of the workshop, you can click on here.

All photos included in this article are provided by courtesy of Tensilica Day 2017.

-

2024.10.21Espressif’s commitment to security through CSA Product Security certification adds significant value, enhancing trust in products built with ESP ZeroCode.

-

2024.09.13Espressif launches ESP RainMaker® in China, enabling customizable, secure IoT deployments with private cloud options for global and local markets.

-

2024.06.13Apple used Espressif’s ESP32-C6, a RISC-V architecture Wi-Fi 6 SoC, to demonstrate use of Embedded Swift to build a smart device that communicates using Matter protocol.

LinkedIn

LinkedIn 微信

微信

Twitter

Twitter Facebook

Facebook